# **ISP1122A**

Universal Serial Bus stand-alone hub

Rev. 01 — 27 March 2000

Preliminary specification

# 1. General description

The ISP1122A is a stand-alone Universal Serial Bus (USB) hub device which complies with *USB Specification Rev. 1.1*. It integrates a Serial Interface Engine (SIE), hub repeater, hub controller, USB data transceivers and a 3.3 V voltage regulator. It has a configurable number of downstream ports, ranging from 2 to 5.

The ISP1122A can be bus-powered, self-powered or hybrid-powered. When it is hybrid-powered the hub functions are powered by the upstream power supply (V<sub>BUS</sub>), but the downstream ports are powered by an external 5 Volt supply. The low power consumption in 'suspend' mode allows easy design of equipment that is compliant with the ACPI™, OnNow™ and USB power management requirements.

The ISP1122A has built-in overcurrent sense inputs, supporting individual and global overcurrent protection for downstream ports. All ports (including the hub) have GoodLink™ indicator outputs for easy visual monitoring of USB traffic. The ISP1122A has a serial I²C-bus interface for external EEPROM access and a reduced frequency (6 MHz) crystal oscillator. These features allow significant cost savings in system design and easy implementation of advanced USB functionality into PC peripherals.

#### 2. Features

- High performance USB hub device with integrated hub repeater, hub controller, Serial Interface Engine (SIE), data transceivers and 3.3 V voltage regulator

- Complies with Universal Serial Bus Specification Rev. 1.1 and ACPI, OnNow and USB power management requirements

- Configurable from 2 to 5 downstream ports with automatic speed detection

- Internal power-on reset and low voltage reset circuit

- Supports bus-powered, hybrid-powered and self-powered application

- Individual or ganged power switching for downstream ports

- Individual or global port overcurrent protection with built-in sense circuits

- 6 MHz crystal oscillator with on-chip PLL for low EMI

- Visual USB traffic monitoring (GoodLink™) for hub and downstream ports

- I<sup>2</sup>C-bus interface to read vendor ID, product ID and configuration bits from external EEPROM

- Operation over the extended USB bus voltage range (4.0 to 5.5 V)

- Operating temperature range -40 to +85 °C

- 8 kV in-circuit ESD protection for lower cost of external components

- Full-scan design with high test coverage

- Available in 32-pin SDIP, SO and LQFP packages.

#### **Ordering information** 3.

Table 1: Ordering information

| Type number | Package | Package                                                              |          |  |  |  |  |  |

|-------------|---------|----------------------------------------------------------------------|----------|--|--|--|--|--|

|             | Name    | Description                                                          | Version  |  |  |  |  |  |

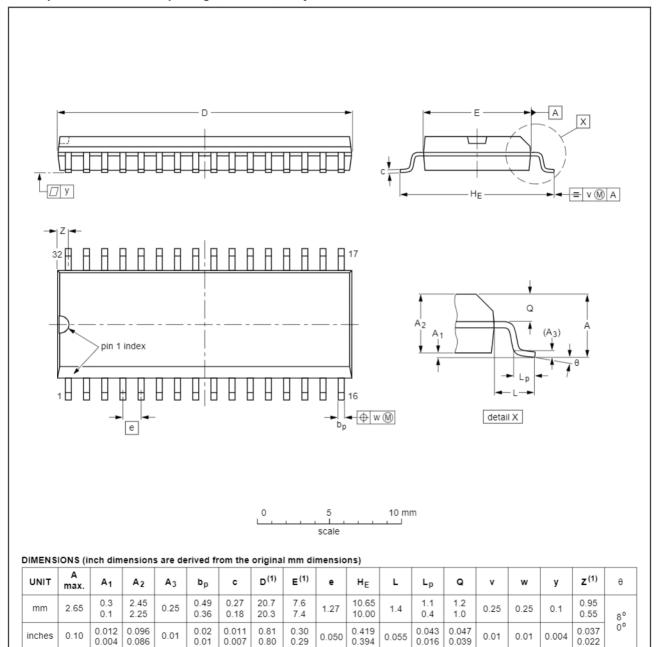

| ISP1122AD   | SO32    | plastic small outline package; 32 leads; body width 7.5 mm           | SOT287-1 |  |  |  |  |  |

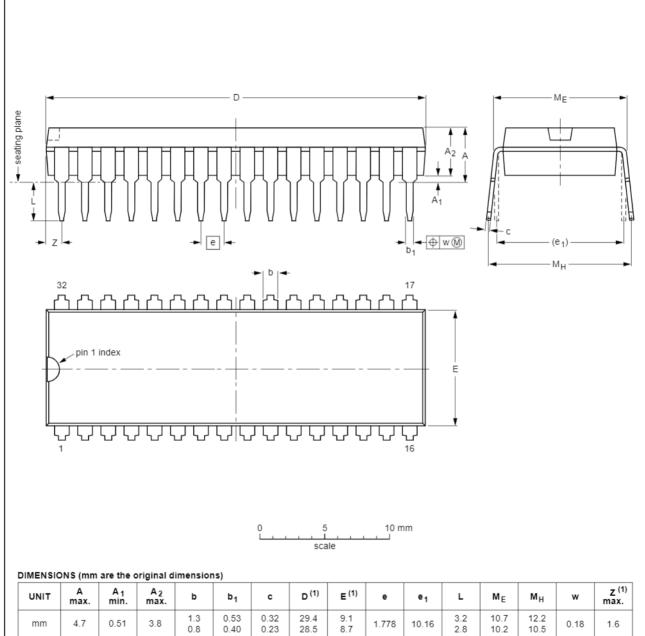

| ISP1122ANB  | SDIP32  | plastic shrink dual in-line package; 32 leads (400 mil)              | SOT232-1 |  |  |  |  |  |

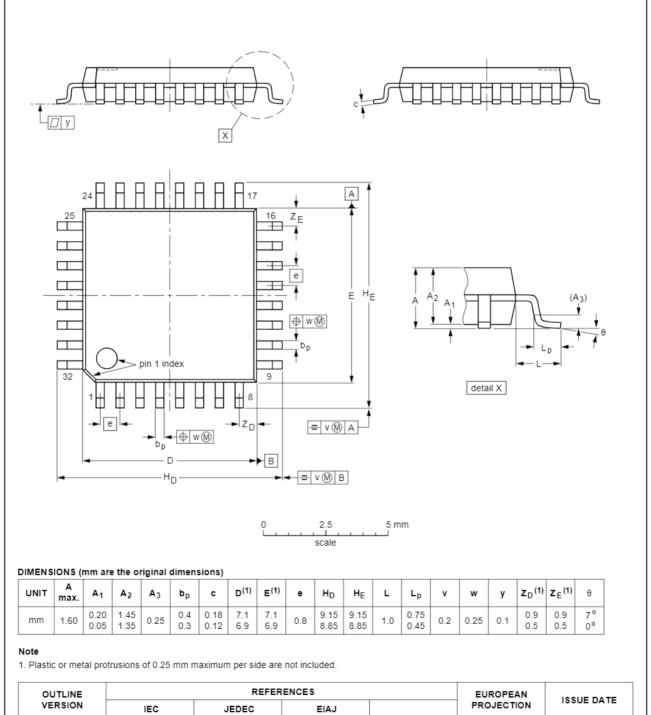

| ISP1122ABD  | LQFP32  | plastic low profile quad flat package; 32 leads; body 7 x 7 x 1.4 mm | SOT358-1 |  |  |  |  |  |

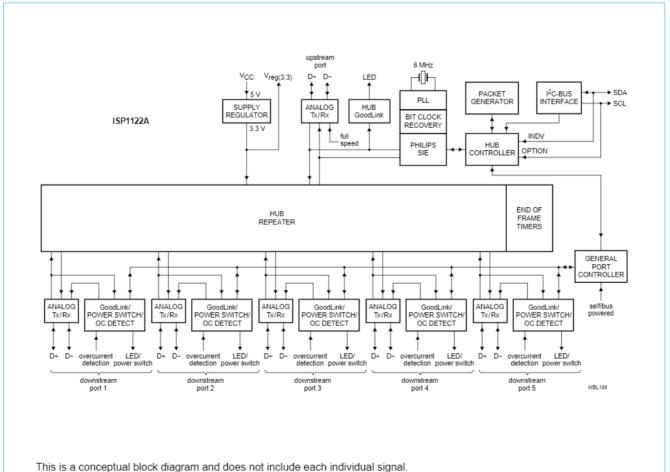

# **Block diagram**

Fig 1. Block diagram.

# 5. Pinning information

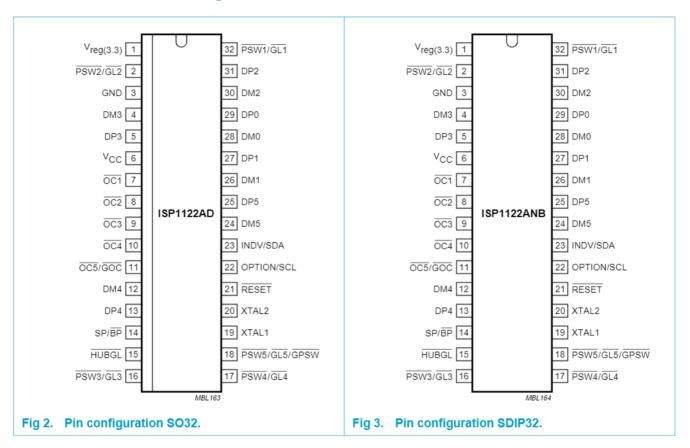

# 5.1 ISP1122AD (SO32) and ISP1122ANB (SDIP32)

### 5.1.1 Pinning

### 5.1.2 Pin description

Table 2: Pin description for SO32 and SDIP32

| Symbol [1]                | Pin | Туре | Description                                                                                                                                   |

|---------------------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>reg(3.3)</sub> [2] | 1   | -    | regulated supply voltage (3.3 V $\pm$ 10%) from internal regulator; used to connect pull-up resistor on DP0 line                              |

| PSW2/GL2 <sup>[3]</sup>   | 2   | 0    | modes 4 to 6: power switch control output for downstream port 2 (open-drain, 6 mA)                                                            |

|                           |     |      | modes 0 to 3, 7: GoodLink LED indicator output for downstream port 2 (open-drain, 6 mA); to connect an LED use a 330 $\Omega$ series resistor |

| GND                       | 3   | -    | ground supply                                                                                                                                 |

| DM3                       | 4   | AI/O | downstream port 3 D- connection (analog) [4]                                                                                                  |

| DP3                       | 5   | AI/O | downstream port 3 D+ connection (analog) [4]                                                                                                  |

| V <sub>CC</sub>           | 6   | -    | supply voltage; connect to USB supply $V_{\text{BUS}}$ (bus-powered or hybrid-powered) or to local supply $V_{\text{DD}}$ (self-powered)      |

| OC1                       | 7   | Al/l | overcurrent sense input for downstream port 1 (analog [5])                                                                                    |

| OC2                       | 8   | Al/l | overcurrent sense input for downstream port 2 (analog [5])                                                                                    |

|                           |     |      |                                                                                                                                               |

Table 2: Pin description for SO32 and SDIP32...continued

| Symbol [1]            | Pin | Туре | Description                                                                                                                                                            |

|-----------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OC3                   | 9   | Al/I | overcurrent sense input for downstream port 3 (analog [5])                                                                                                             |

| OC4                   | 10  | Al/I | overcurrent sense input for downstream port 4 (analog [5])                                                                                                             |

| OC5/GOC [3]           | 11  | Al/l | <b>modes 5, 7</b> : overcurrent sense input for downstream port 5 (analog <sup>[5]</sup> )                                                                             |

|                       |     |      | modes 0, 1, 3: global overcurrent sense input (analog [5])                                                                                                             |

| DM4                   | 12  | AI/O | downstream port 4 D- connection (analog) <sup>[4]</sup>                                                                                                                |

| DP4                   | 13  | AI/O | downstream port 4 D+ connection (analog) [4]                                                                                                                           |

| SP/BP                 | 14  | I    | selects power mode:                                                                                                                                                    |

|                       |     |      | $\textbf{self-powered}:$ connect to $V_{\text{DD}}$ (local power supply); also use this mode for hybrid-powered operation                                              |

|                       |     |      | <b>bus-powered</b> : connect to GND; disable downstream port 5 to meet supply current requirements [4]                                                                 |

| HUBGL                 | 15  | 0    | hub GoodLink LED indicator output (open-drain, 6 mA); to connect an LED use a 330 $\Omega$ series resistor; if unused connect to $V_{CC}$ via a 10 k $\Omega$ resistor |

| PSW3/GL3[3]           | 16  | 0    | modes 4 to 6: power switch control output for downstream port 3 (open-drain, 6 mA)                                                                                     |

|                       |     |      | modes 0 to 3, 7: GoodLink LED indicator output for downstream port 3 (open-drain, 6 mA); to connect an LED use a 330 $\Omega$ series resistor                          |

| PSW4/GL4 [3]          | 17  | 0    | modes 4 to 6: power switch control output for downstream port 4 (open-drain, 6 mA)                                                                                     |

|                       |     |      | modes 0 to 3, 7: GoodLink LED indicator output for downstream port 4 (open-drain, 6 mA); to connect an LED use a 330 $\Omega$ series resistor                          |

| PSW5/GL5/<br>GPSW [3] | 18  | 0    | <b>mode 5</b> : power switch control output for downstream port 5 (open-drain, 6 mA)                                                                                   |

|                       |     |      | modes 3, 7: GoodLink LED indicator output for downstream port 5 (open-drain, 6 mA); to connect an LED use a 330 $\Omega$ series resistor                               |

|                       |     |      | modes 0 to 2: gang mode power switch control output (open-drain, 6 mA)                                                                                                 |

| XTAL1                 | 19  | I    | crystal oscillator input (6 MHz)                                                                                                                                       |

| XTAL2                 | 20  | 0    | crystal oscillator output (6 MHz)                                                                                                                                      |

| RESET [2]             | 21  | I    | reset input (Schmitt trigger); a LOW level produces an asynchronous reset; connect to $V_{\text{CC}}$ for power-on reset (internal POR circuit)                        |

| OPTION/SCL            | 22  | I/O  | mode selection input; also functions as I <sup>2</sup> C-bus clock output (open-drain, 6 mA)                                                                           |

| INDV/SDA              | 23  | I/O  | selects individual (HIGH) or global (LOW) power switching and overcurrent detection; also functions as bidirectional I <sup>2</sup> C-bus data line (open-drain, 6 mA) |

| DM5                   | 24  | AI/O | downstream port 5 D- connection (analog) [4]                                                                                                                           |

| DP5                   | 25  | AI/O | downstream port 5 D+ connection (analog) [4]                                                                                                                           |

| DM1                   | 26  | AI/O | downstream port 1 D- connection (analog) [6]                                                                                                                           |

| DP1                   | 27  | AI/O | downstream port 1 D+ connection (analog) [6]                                                                                                                           |

4 of 48

Table 2: Pin description for SO32 and SDIP32...continued

| Symbol [1]              | Pin | Туре | Description                                                                                                                                   |

|-------------------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| DM0                     | 28  | AI/O | upstream port D- connection (analog)                                                                                                          |

| DP0                     | 29  | AI/O | upstream port D+ connection (analog)                                                                                                          |

| DM2                     | 30  | AI/O | downstream port 2 D- connection (analog) [6]                                                                                                  |

| DP2                     | 31  | AI/O | downstream port 2 D+ connection (analog) [6]                                                                                                  |

| PSW1/GL1 <sup>[3]</sup> | 32  | 0    | modes 4 to 6: power switch control output for downstream port 1 (open-drain, 6 mA)                                                            |

|                         |     |      | modes 0 to 3, 7: GoodLink LED indicator output for downstream port 1 (open-drain, 6 mA); to connect an LED use a 330 $\Omega$ series resistor |

- [1] Symbol names with an overscore (e.g. NAME) indicate active LOW signals.

- [2] The voltage at pin V<sub>reg(3.3)</sub> is gated by the RESET pin. This allows fully self-powered operation by connecting RESET to V<sub>BUS</sub> (+5 V USB supply). If V<sub>BUS</sub> is lost upstream port D+ will not be driven.

- [3] See Table 4 "Mode selection".

- [4] To disable a downstream port connect both D+ and D- to  $V_{CC}$  via a 1 M $\Omega$  resistor; unused ports must be disabled in reverse order starting from port 5.

- [5] Analog detection circuit can be switched off using an external EEPROM, see Table 23; in this case, the pin functions as a logic input (TTL level).

- [6] Downstream ports 1 and 2 cannot be disabled.

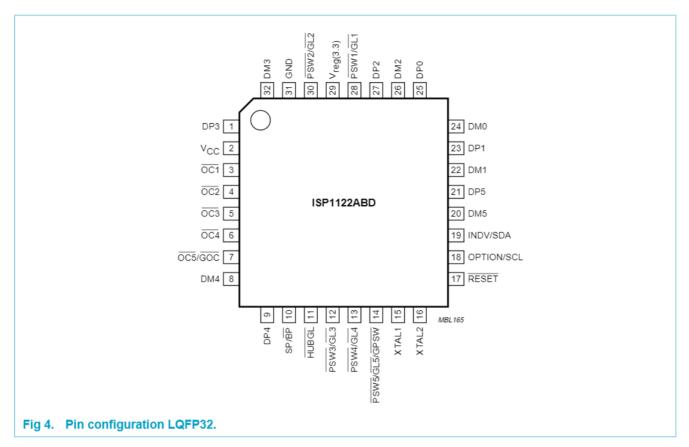

# 5.2 ISP1122ABD (LQFP32)

### 5.2.1 Pinning

## 5.2.2 Pin description

Table 3: Pin description for LQFP32

| Symbol [1]                | Pin | Туре | Description                                                                                                                                   |

|---------------------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>reg(3.3)</sub> [2] | 29  | -    | regulated supply voltage (3.3 V $\pm$ 10%) from internal regulator; used to connect pull-up resistor on DP0 line                              |

| PSW2/GL2[3]               | 30  | 0    | modes 4 to 6: power switch control output for downstream port 2 (open-drain, 6 mA)                                                            |

|                           |     |      | modes 0 to 3, 7: GoodLink LED indicator output for downstream port 2 (open-drain, 6 mA); to connect an LED use a 330 $\Omega$ series resistor |

| GND                       | 31  | -    | ground supply                                                                                                                                 |

| DM3                       | 32  | AI/O | downstream port 3 D- connection (analog) <sup>[4]</sup>                                                                                       |

| DP3                       | 1   | AI/O | downstream port 3 D+ connection (analog)[4]                                                                                                   |

| V <sub>CC</sub>           | 2   | -    | supply voltage; connect to USB supply $V_{\text{BUS}}$ (bus-powered or hybrid-powered) or to local supply $V_{\text{DD}}$ (self-powered)      |

| OC1                       | 3   | Al/I | overcurrent sense input for downstream port 1 (analog [5])                                                                                    |

| OC2                       | 4   | Al/I | overcurrent sense input for downstream port 2 (analog [5])                                                                                    |

| OC3                       | 5   | Al/l | overcurrent sense input for downstream port 3 (analog [5])                                                                                    |

| OC4                       | 6   | Al/I | overcurrent sense input for downstream port 4 (analog [5])                                                                                    |

|                           |     |      |                                                                                                                                               |

Table 3: Pin description for LQFP32...continued

|                         |     |      | r LQFP32continued                                                                                                                                                      |

|-------------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol [1]              | Pin | Туре | Description                                                                                                                                                            |

| OC5/GOC [3]             | 7   | AI/I | <b>modes 5, 7</b> : overcurrent sense input for downstream port 5 (analog <sup>[5]</sup> )                                                                             |

|                         |     |      | modes 0, 1, 3: global overcurrent sense input (analog [5])                                                                                                             |

| DM4                     | 8   | AI/O | downstream port 4 D- connection (analog) <sup>[4]</sup>                                                                                                                |

| DP4                     | 9   | AI/O | downstream port 4 D+ connection (analog) <sup>[4]</sup>                                                                                                                |

| SP/BP                   | 10  | I    | selects power mode:                                                                                                                                                    |

|                         |     |      | $\textbf{self-powered}:$ connect to $V_{\text{DD}}$ (local power supply); also use this mode for hybrid-powered operation                                              |

|                         |     |      | <b>bus-powered</b> : connect to GND; disable downstream port 5 to meet supply current requirements [4]                                                                 |

| HUBGL                   | 11  | 0    | hub GoodLink LED indicator output (open-drain, 6 mA); to connect an LED use a 330 $\Omega$ series resistor; if unused connect to $V_{CC}$ via a 10 k $\Omega$ resistor |

| PSW3/GL3 <sup>[3]</sup> | 12  | Ο    | modes 4 to 6: power switch control output for downstream port 3 (open-drain, 6 mA)                                                                                     |

|                         |     |      | modes 0 to 3, 7: GoodLink LED indicator output for downstream port 3 (open-drain, 6 mA); to connect an LED use a 330 $\Omega$ series resistor                          |

| PSW4/GL4 <sup>[3]</sup> | 13  | 0    | modes 4 to 6: power switch control output for downstream port 4 (open-drain, 6 mA)                                                                                     |

|                         |     |      | modes 0 to 3, 7: GoodLink LED indicator output for downstream port 4 (open-drain, 6 mA); to connect an LED use a 330 $\Omega$ series resistor                          |

| PSW5/GL5/<br>GPSW[3]    | 14  | 0    | mode 5: power switch control output for downstream port 5 (open-drain, 6 mA)                                                                                           |

|                         |     |      | modes 3, 7: GoodLink LED indicator output for downstream port 5 (open-drain, 6 mA); to connect an LED use a 330 $\Omega$ series resistor                               |

|                         |     |      | modes 0 to 2: gang mode power switch control output (open-drain, 6 mA)                                                                                                 |

| XTAL1                   | 15  | I    | crystal oscillator input (6 MHz)                                                                                                                                       |

| XTAL2                   | 16  | 0    | crystal oscillator output (6 MHz)                                                                                                                                      |

| RESET [2]               | 17  | I    | reset input (Schmitt trigger); a LOW level produces an asynchronous reset; connect to $V_{\text{CC}}$ for power-on reset (internal POR circuit)                        |

| OPTION/SCL              | 18  | I/O  | mode selection input; also functions as I <sup>2</sup> C-bus clock output (open-drain, 6 mA)                                                                           |

| INDV/SDA                | 19  | I/O  | selects individual (HIGH) or global (LOW) power switching and overcurrent detection; also functions as bidirectional I <sup>2</sup> C-bus data line (open-drain, 6 mA) |

| DM5                     | 20  | AI/O | downstream port 5 D- connection (analog) <sup>[4]</sup>                                                                                                                |

| DP5                     | 21  | AI/O | downstream port 5 D+ connection (analog) <sup>[4]</sup>                                                                                                                |

| DM1                     | 22  | AI/O | downstream port 1 D- connection (analog) [6]                                                                                                                           |

| DP1                     | 23  | AI/O | downstream port 1 D+ connection (analog) [6]                                                                                                                           |

| DM0                     | 24  | AI/O | upstream port D- connection (analog)                                                                                                                                   |

| DP0                     | 25  | AI/O | upstream port D+ connection (analog)                                                                                                                                   |

|                         |     |      |                                                                                                                                                                        |

Table 3: Pin description for LQFP32...continued

| Symbol [1]   | Pin | Туре | Description                                                                                                                                   |

|--------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| DM2          | 26  | AI/O | downstream port 2 D- connection (analog) [6]                                                                                                  |

| DP2          | 27  | AI/O | downstream port 2 D+ connection (analog) [6]                                                                                                  |

| PSW1/GL1 [3] | 28  | 0    | modes 4 to 6: power switch control output for downstream port 1 (open-drain, 6 mA)                                                            |

|              |     |      | modes 0 to 3, 7: GoodLink LED indicator output for downstream port 1 (open-drain, 6 mA); to connect an LED use a 330 $\Omega$ series resistor |

- [1] Symbol names with an overscore (e.g. NAME) indicate active LOW signals.

- [2] The voltage at pin V<sub>reg(3.3)</sub> is gated by the RESET pin. This allows fully self-powered operation by connecting RESET to V<sub>BUS</sub> (+5 V USB supply). If V<sub>BUS</sub> is lost upstream port D+ will not be driven.

- [3] See Table 4 "Mode selection".

- [4] To disable a downstream port connect both D+ and D- to V<sub>CC</sub> via a 1 MΩ resistor; unused ports must be disabled in reverse order starting from port 5.

- [5] Analog detection circuit can be switched off using an external EEPROM, see Table 23; in this case, the pin functions as a logic input (TTL level).

- [6] Downstream ports 1 and 2 cannot be disabled.

# 6. Functional description

The ISP1122A is a stand-alone USB hub with up to 5 downstream ports. The number of ports can be configured between 2 and 5. The downstream ports can be used to connect low-speed or full-speed USB peripherals. All standard USB requests from the host are handled by the hardware without the need for firmware intervention. The block diagram is shown in Figure 1.

The ISP1122A requires only a single supply voltage. An internal 3.3 V regulator provides the supply voltage for the analog USB data transceivers.

The ISP1122A supports both bus-powered and self-powered hub operation. When using bus-powered operation a downstream port cannot supply more than 100 mA to a peripheral. In case of self-powered operation an external supply is used to power the downstream ports, allowing a current consumption of max. 500 mA per port.

A basic I<sup>2</sup>C-bus interface is provided for reading vendor ID, product ID and configuration bits from an external EEPROM upon a reset.

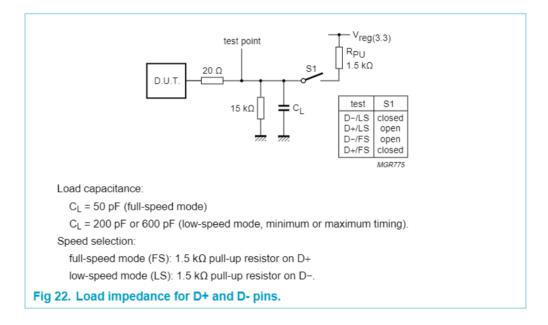

# 6.1 Analog transceivers

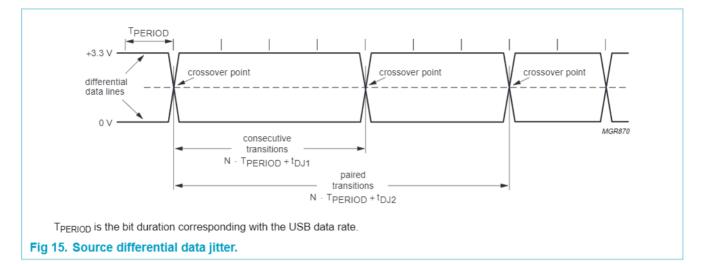

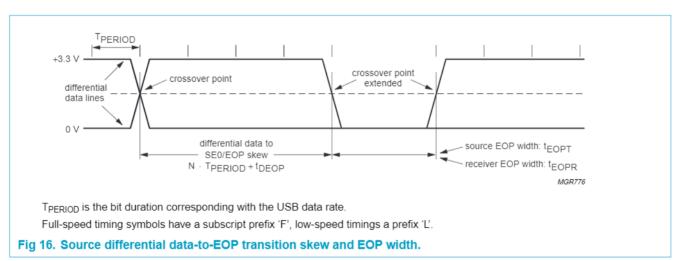

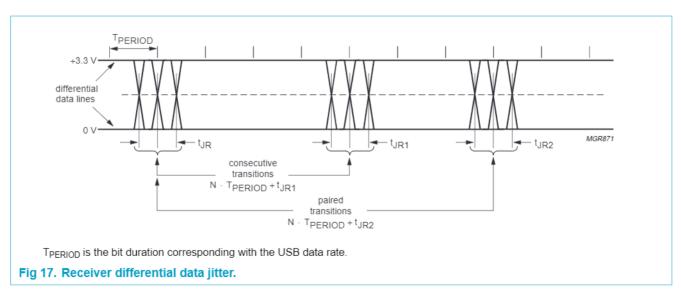

The integrated transceiver interfaces directly to the USB cables through external termination resistors. They are capable of transmitting and receiving serial data at both 'full-speed' (12 Mbit/s) and 'low-speed' (1.5 Mbit/s) data rates. The slew rates are adjusted according to the speed of the device connected and lie within the range mentioned in the *USB Specification Rev. 1.1*.

# 6.2 Philips Serial Interface Engine (SIE)

The Philips SIE implements the full USB protocol layer. It is completely hardwired for speed and needs no firmware intervention. The functions of this block include: synchronization pattern recognition, parallel/serial conversion, bit (de-)stuffing, CRC checking/generation, Packet IDentifier (PID) verification/generation, address recognition, handshake evaluation/generation.

### 6.3 Hub repeater

The hub repeater is responsible for managing connectivity on a 'per packet' basis. It implements 'packet signalling' and 'resume' connectivity. Low-speed devices can be connected to downstream ports. If a low-speed device is detected the repeater will not propagate upstream packets to the corresponding port, unless they are preceded by a PREAMBLE PID.

#### 6.4 End-of-frame timers

This block contains the specified EOF1 and EOF2 timers which are used to detect 'loss-of-activity' and 'babble' error conditions in the hub repeater. The timers also maintain the low-speed keep-alive strobe which is sent at the beginning of a frame.

# 6.5 General and individual port controller

The general and individual port controllers together provide status and control of individual downstream ports. Any port status change will be reported to the host via the hub status change (interrupt) endpoint.

#### 6.6 GoodLink

Indication of a good USB connection is provided through GoodLink technology. An LED can be directly connected via an external 330  $\Omega$  resistor.

During enumeration the LED blinks on momentarily. After successful configuration of the ISP1122A, the LED is permanently on. The LED blinks off for 100 ms upon each successful packet transfer (with ACK). The hub GoodLink indicator blinks when the hub receives a packet addressed to it. Downstream GoodLink indicators blink upon an acknowledgment from the associated port. In 'suspend' mode the LED is off.

This feature provides a user-friendly indication of the status of the hub, the connected downstream devices and the USB traffic. It is a useful diagnostics tool to isolate faulty USB equipment and helps to reduce field support and hotline costs.

## 6.7 Bit clock recovery

The bit clock recovery circuit recovers the clock from the incoming USB data stream using a 4 · oversampling principle. It is able to track jitter and frequency drift as specified by the *USB Specification Rev. 1.1*.

### 6.8 Voltage regulator

A 5 to 3.3 V DC-DC regulator is integrated on-chip to supply the analog transceiver and internal logic. This can also be used to supply the terminal 1.5 k $\Omega$  pull-up resistor on the D+ line of the upstream connection.

9397 750 06986

# 6.9 PLL clock multiplier

A 6 to 48 MHz clock multiplier Phase-Locked Loop (PLL) is integrated on-chip. This allows for the use of low-cost 6 MHz crystals. The low crystal frequency also minimizes Electro-Magnetic Interference (EMI). The PLL requires no external components.

#### 6.10 Overcurrent detection

An overcurrent detection circuit for downstream ports has been integrated on-chip. It is self-reporting, resets automatically, has a low trip time and requires no external components. Both individual and global overcurrent detection are supported.

### 6.11 I<sup>2</sup>C-bus interface

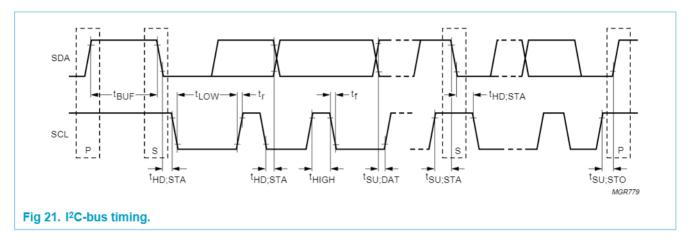

A basic serial I<sup>2</sup>C-bus interface (single master, 100 kHz) is provided to read VID, PID and configuration bits from an external I<sup>2</sup>C-bus EEPROM (e.g. Philips PCF8582 or equivalent). At reset the ISP1122A reads 6 bytes of data from the external memory.

The I<sup>2</sup>C-bus interface timing complies with the standard mode of operation as described in *The I<sup>2</sup>C-bus and how to use it*, order number 9398 393 40011.

# 7. Modes of operation

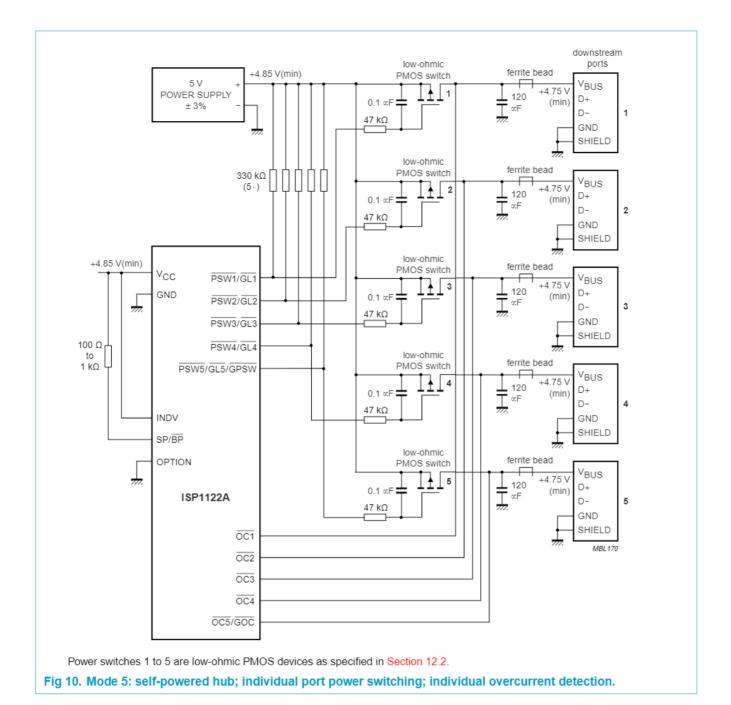

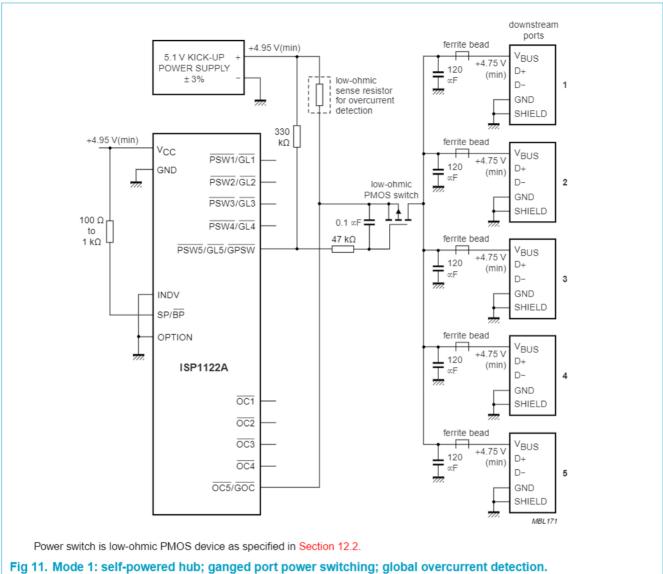

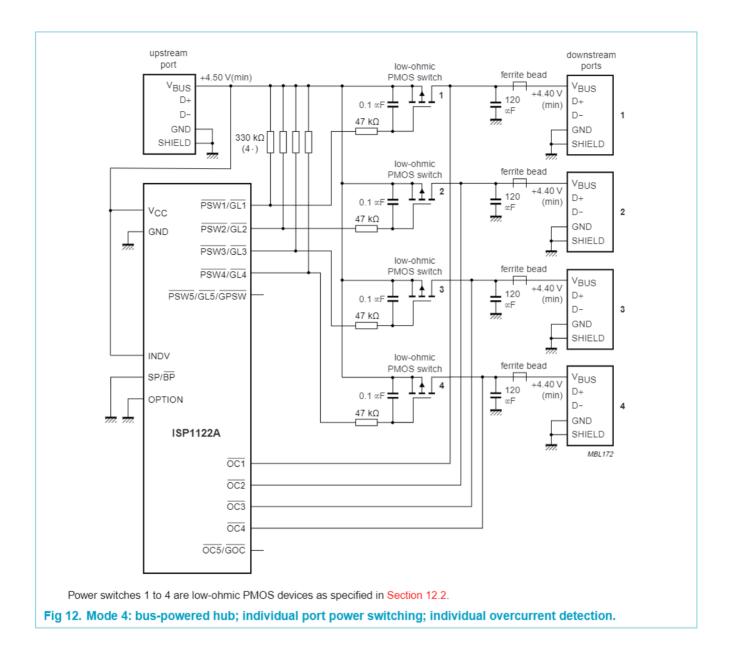

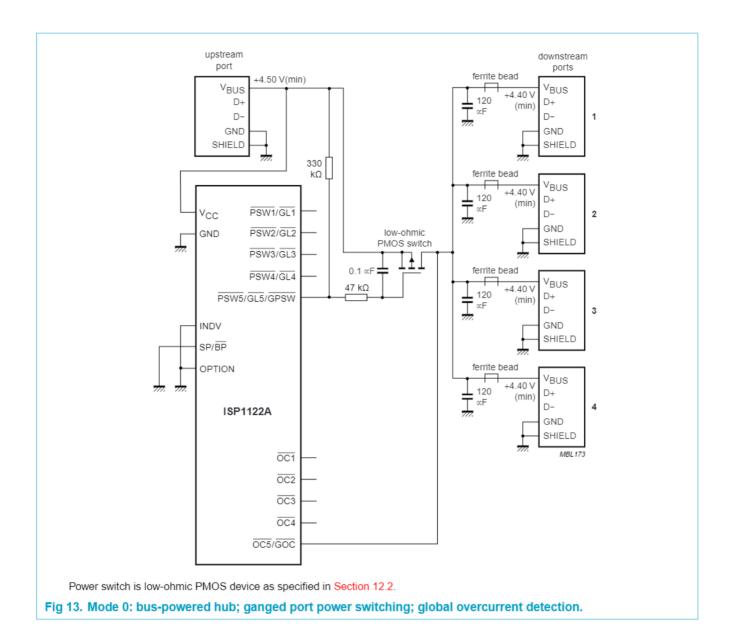

The ISP1122A has several modes of operation, each corresponding with a different pin configuration. Modes are selected by means of pins INDV, OPTION and SP/BP, as shown in Table 4.

Table 4: Mode selection

| Mode | INDV<br>[1] | OPTION | SP/BP | PSWn/GLn<br>(n = 1 to 4) | PSW5/GL5/GPSW    | OCn<br>(n = 1 to 4)       | OC5/GOC                   |

|------|-------------|--------|-------|--------------------------|------------------|---------------------------|---------------------------|

| 0    | 0           | 0      | 0     | GoodLink                 | ganged power     | inactive                  | global overcurrent        |

| 1    | 0           | 0      | 1     | GoodLink                 | ganged power     | inactive                  | global overcurrent        |

| 2    | 0           | 1      | 0     | GoodLink                 | ganged power     | inactive [3]              | inactive [3]              |

| 3    | 0           | 1      | 1     | GoodLink [4]             | GoodLink [4]     | inactive                  | global overcurrent        |

| 4    | 1           | 0      | 0     | individual power         | inactive         | individual<br>overcurrent | inactive                  |

| 5    | 1           | 0      | 1     | individual power         | individual power | individual overcurrent    | individual<br>overcurrent |

| 6    | 1           | 1      | 0     | individual power         | inactive         | inactive [3]              | inactive [3]              |

| 7    | 1           | 1      | 1     | GoodLink [4]             | GoodLink [4]     | individual<br>overcurrent | individual<br>overcurrent |

- [1] Port power switching: logic 0 = ganged, logic 1 = individual.

- [2] Power mode: logic 0 = bus-powered, logic 1 = self-powered (or hybrid-powered).

- [3] No overcurrent detection.

- [4] No power switching

# 8. Endpoint descriptions

Each USB device is logically composed of several independent endpoints. An endpoint acts as a terminus of a communication flow between the host and the device. At design time each endpoint is assigned a unique number (endpoint identifier, see Table 5). The combination of the device address (given by the host during enumeration), the endpoint number and the transfer direction allows each endpoint to be uniquely referenced.

The ISP1122A has two endpoints, endpoint 0 (control) and endpoint 1 (interrupt).

Table 5: Hub endpoints

| Function | Ports                             | Endpoint identifier | Transfer<br>type | Direction [1] | Max. packet size (bytes) |

|----------|-----------------------------------|---------------------|------------------|---------------|--------------------------|

| Hub      | 0: upotroom                       | 0                   | control          | OUT           | 64                       |

|          | 0: upstream<br>1 to 5: downstream | U                   | COTILIOI         | IN            | 64                       |

|          | i to 5. downstream                | 1                   | interrupt        | IN            | 1                        |

<sup>[1]</sup> IN: input for the USB host; OUT: output from the USB host.

# 8.1 Hub endpoint 0 (control)

All USB devices and functions must implement a default control endpoint (ID = 0). This endpoint is used by the host to configure the device and to perform generic USB status and control access.

The ISP1122A hub supports the following USB descriptor information through its control endpoint 0, which can handle transfers of 64 bytes maximum:

- · Device descriptor

- · Configuration descriptor

- · Interface descriptor

- · Endpoint descriptor

- · Hub descriptor

- String descriptor.

# 8.2 Hub endpoint 1 (interrupt)

Endpoint 1 is used by the ISP1122A hub to provide status change information to the host. This endpoint can be accessed only after the hub has been configured by the host (by sending the Set Configuration command).

Endpoint 1 is an interrupt endpoint: the host polls it once every 255 ms by sending an IN token. If the hub has detected no change in the port status it returns a NAK (Not AcKnowledge) response to this request, otherwise it sends the Status Change byte (see Table 6).

Table 6: Status Change byte: bit allocation

| Bit | Symbol    | Description                                                    |

|-----|-----------|----------------------------------------------------------------|

| 0   | Hub SC    | a logic 1 indicates a status change on the hub's upstream port |

| 1   | Port 1 SC | a logic 1 indicates a status change on downstream port 1       |

| 2   | Port 2 SC | a logic 1 indicates a status change on downstream port 2       |

| 3   | Port 3 SC | a logic 1 indicates a status change on downstream port 3       |

| 4   | Port 4 SC | a logic 1 indicates a status change on downstream port 4       |

| 5   | Port 5 SC | a logic 1 indicates a status change on downstream port 5       |

| 6   | reserved  | not used                                                       |

| 7   | reserved  | not used                                                       |

# 9. Host requests

The ISP1122A handles all standard USB requests from the host via control endpoint 0. The control endpoint can handle a maximum of 64 bytes per transfer.

**Remark:** Please note that the USB data transmission order is Least Significant Bit (LSB) first. In the following tables multi-byte variables are displayed least significant byte first.

# 9.1 Standard requests

Table 7 shows the supported standard USB requests. Some requests are explicitly unsupported. All other requests will be responded with a STALL packet.

Table 7: Standard USB requests

| Request name                    | bmRequestType         | bRequest        | wValue                 | windex             | wLength               | Data                                                       |

|---------------------------------|-----------------------|-----------------|------------------------|--------------------|-----------------------|------------------------------------------------------------|

| Request name                    | byte 0 [7:0]<br>(Bin) | byte 1<br>(Hex) | byte 2, 3<br>(Hex)     | byte 4, 5<br>(Hex) | byte 6, 7<br>(Hex)    | Duta                                                       |

| Address                         |                       |                 |                        |                    |                       |                                                            |

| Set Address                     | X000 0000             | 05              | address <sup>[1]</sup> | 00, 00             | 00, 00                | none                                                       |

| Configuration                   |                       |                 |                        |                    |                       |                                                            |

| Get Configuration               | 1000 0000             | 08              | 00, 00                 | 00, 00             | 01, 00                | configuration<br>value = 01H                               |

| Set Configuration (0)           | X000 0000             | 09              | 00, 00                 | 00, 00             | 00, 00                | none                                                       |

| Set Configuration (1)           | X000 0000             | 09              | 01, 00                 | 00, 00             | 00, 00                | none                                                       |

| Descriptor                      |                       |                 |                        |                    |                       |                                                            |

| Get Configuration<br>Descriptor | 1000 0000             | 06              | 00, 02                 | 00, 00             | length <sup>[2]</sup> | configuration,<br>interface and<br>endpoint<br>descriptors |

| Get Device Descriptor           | 1000 0000             | 06              | 00, 01                 | 00, 00             | length <sup>[2]</sup> | device<br>descriptor                                       |

| Get String Descriptor (0)       | 1000 0000             | 06              | 03, 00                 | 00, 00             | length <sup>[2]</sup> | language ID<br>string                                      |

| Get String Descriptor (1)       | 1000 0000             | 06              | 03, 01                 | 00, 00             | length <sup>[2]</sup> | manufacturer<br>string                                     |

| Get String Descriptor (2)       | 1000 0000             | 06              | 03, 02                 | 00, 00             | length [2]            | product string                                             |

Table 7: Standard USB requests...continued

| Request name                               | bmRequestType<br>byte 0 [7:0]<br>(Bin) | bRequest<br>byte 1<br>(Hex) | wValue<br>byte 2, 3<br>(Hex) | windex<br>byte 4, 5<br>(Hex) | wLength<br>byte 6, 7<br>(Hex) | Data                 |

|--------------------------------------------|----------------------------------------|-----------------------------|------------------------------|------------------------------|-------------------------------|----------------------|

| Feature                                    |                                        |                             |                              |                              |                               |                      |

| Clear Device Feature (REMOTE_WAKEUP)       | X000 0000                              | 01                          | 01, 00                       | 00, 00                       | 00, 00                        | none                 |

| Clear Endpoint (1)<br>Feature (HALT/STALL) | X000 0010                              | 01                          | 00, 00                       | 81, 00                       | 00, 00                        | none                 |

| Set Device Feature (REMOTE_WAKEUP)         | X000 0000                              | 03                          | 01, 00                       | 00, 00                       | 00, 00                        | none                 |

| Set Endpoint (1)<br>Feature (HALT/STALL)   | X000 0010                              | 03                          | 00, 00                       | 81, 00                       | 00, 00                        | none                 |

| Status                                     |                                        |                             |                              |                              |                               |                      |

| Get Device Status                          | 1000 0000                              | 00                          | 00, 00                       | 00, 00                       | 02, 00                        | device status        |

| Get Interface Status                       | 1000 0001                              | 00                          | 00, 00                       | 00, 00                       | 02, 00                        | zero                 |

| Get Endpoint (0) Status                    | 1000 0010                              | 00                          | 00, 00                       | 00/80[3], 00                 | 02, 00                        | endpoint 0<br>status |

| Get Endpoint (1) Status                    | 1000 0010                              | 00                          | 00, 00                       | 81, 00                       | 02, 00                        | endpoint 1<br>status |

| Unsupported                                |                                        |                             |                              |                              |                               |                      |

| Set Descriptor                             | 0000 0000                              | 07                          | XX, XX                       | XX, XX                       | XX, XX                        | descriptor;<br>STALL |

| Get Interface                              | 1000 0001                              | 0A                          | 00, 00                       | XX, XX                       | 01, 00                        | STALL                |

| Set Interface                              | X000 0001                              | 0B                          | XX, XX                       | XX, XX                       | 00, 00                        | STALL                |

| Synch Frame                                | 1000 0010                              | 0C                          | 00, 00                       | XX, XX                       | 02, 00                        | STALL                |

<sup>[1]</sup> Device address: 0 to 127.

# 9.2 Hub specific requests

In Table 8 the supported hub specific requests are listed, as well as some unsupported requests. Table 9 provides the feature selectors for setting or clearing port features.

Table 8: Hub specific requests

| Request name                           | bmRequestType<br>byte 0 [7:0]<br>(Bin) | bRequest<br>byte 1<br>(Hex) | wValue<br>byte 2, 3<br>(Hex) | windex<br>byte 4, 5<br>(Hex) | wLength<br>byte 6, 7<br>(Hex) | Data           |

|----------------------------------------|----------------------------------------|-----------------------------|------------------------------|------------------------------|-------------------------------|----------------|

| Descriptor                             |                                        |                             |                              |                              |                               |                |

| Get Hub Descriptor                     | 1010 0000                              | 06                          | 00, 00/29[1]                 | 00, 00                       | length [2], 00                | hub descriptor |

| Feature                                |                                        |                             |                              |                              |                               |                |

| Clear Hub Feature<br>(C_LOCAL_POWER)   | X010 0000                              | 01                          | 00, 00                       | 00, 00                       | 00, 00                        | none           |

| Clear Port Feature (feature selectors) | X010 0011                              | 01                          | feature [3], 00              | port <sup>[4]</sup> , 00     | 00, 00                        | none           |

| Set Port Feature (feature selectors)   | X010 0011                              | 03                          | feature [3], 00              | port <sup>[4]</sup> , 00     | 00, 00                        | none           |

Preliminary specification

9397 750 06986

© Philips Electronics N.V. 2000. All rights reserved.

<sup>[2]</sup> Returned value in bytes.

<sup>[3]</sup> MSB specifies endpoint direction: 0 = OUT, 1 = IN. The ISP1122A accepts either value.

Table 8: Hub specific requests...continued

| Request name                          | bmRequestType<br>byte 0 [7:0]<br>(Bin) | bRequest<br>byte 1<br>(Hex) | wValue<br>byte 2, 3<br>(Hex) | windex<br>byte 4, 5<br>(Hex) | wLength<br>byte 6, 7<br>(Hex) | Data                                     |

|---------------------------------------|----------------------------------------|-----------------------------|------------------------------|------------------------------|-------------------------------|------------------------------------------|

| Status                                |                                        |                             |                              |                              |                               |                                          |

| Get Hub Status                        | 1010 0000                              | 00                          | 00, 00                       | 00, 00                       | 04, 00                        | hub status and<br>status change<br>field |

| Get Port Status                       | 1010 0011                              | 00                          | 00, 00                       | port <sup>[4]</sup> , 00     | 04, 00                        | port status                              |

| Unsupported                           |                                        |                             |                              |                              |                               |                                          |

| Get Bus Status                        | 1010 0011                              | 02                          | 00, 00                       | port [4], 00                 | 01, 00                        | STALL                                    |

| Clear Hub Feature<br>(C_OVER_CURRENT) | X010 0000                              | 01                          | 01, 00                       | 00, 00                       | 00, 00                        | STALL                                    |

| Set Hub Descriptor                    | 0010 0000                              | 07                          | XX, XX                       | 00, 00                       | 3E, 00                        | STALL                                    |

| Set Hub Feature<br>(C_LOCAL_POWER)    | X010 0000                              | 03                          | 00, 00                       | 00, 00                       | 00, 00                        | STALL                                    |

| Set Hub Feature<br>(C_OVER_CURRENT)   | X010 0000                              | 03                          | 01, 00                       | 00, 00                       | 00, 00                        | STALL                                    |

<sup>[1]</sup> USB Specification Rev. 1.0 uses 00H, USB Specification Rev. 1.1 specifies 29H.

Table 9: Port feature selectors

| Feature selector name | Value (Hex) | Set feature               | Clear feature                      |

|-----------------------|-------------|---------------------------|------------------------------------|

| PORT_CONNECTION       | 00          | not used                  | not used                           |

| PORT_ENABLE           | 01          | not used                  | disables a port                    |

| PORT_SUSPEND          | 02          | suspends a port           | resumes a port                     |

| PORT_OVERCURRENT      | 03          | not used                  | not used                           |

| PORT_RESET            | 04          | resets and enables a port | not used                           |

| PORT_POWER            | 08          | powers on a port          | powers off a port                  |

| PORT_LOW_SPEED        | 09          | not used                  | not used                           |

| C_PORT_CONNECTION     | 10          | not used                  | clears port connection change bit  |

| C_PORT_ENABLE         | 11          | not used                  | clears port enable change bit      |

| C_PORT_SUSPEND        | 12          | not used                  | clears port suspend change bit     |

| C_PORT_OVERCURRENT    | 13          | not used                  | clears port overcurrent change bit |

| C_PORT_RESET          | 14          | not used                  | clears port reset change bit       |

|                       |             |                           |                                    |

<sup>[2]</sup> Returned value in bytes.

<sup>[3]</sup> Feature selector value, see Table 9.

<sup>[4]</sup> Downstream port identifier: 1 to N with N = number of enabled ports (2 to 5).

# 9.3 Descriptors

The ISP1122A hub controller supports the following standard USB descriptors:

- Device

- Configuration

- Interface

- Endpoint

- Hub

- · String.

Table 10: Device descriptor

Values in square brackets are optional.

| Offset<br>(bytes) | Field name         | Size<br>(bytes) | Value<br>(Hex) | Comments                                                                                           |

|-------------------|--------------------|-----------------|----------------|----------------------------------------------------------------------------------------------------|

| 0                 | bLength            | 1               | 12             | descriptor length = 18 bytes                                                                       |

| 1                 | bDescriptorType    | 1               | 01             | type = DEVICE                                                                                      |

| 2                 | bcdUSB             | 2               | 10, 01         | USB Specification Rev. 1.1                                                                         |

| 4                 | bDeviceClass       | 1               | 09             | HUB_CLASSCODE                                                                                      |

| 5                 | bDeviceSubClass    | 1               | 00             | -                                                                                                  |

| 6                 | bDeviceProtocol    | 1               | 00             | -                                                                                                  |

| 7                 | bMaxPacketSize0    | 1               | 40             | packet size = 64 bytes                                                                             |

| 8                 | idVendor           | 2               | CC, 04         | Philips Semiconductors vendor ID (04CC); can be customized using an external EEPROM (see Table 23) |

| 10                | idProduct          | 2               | 22, 11         | ISP1122A product ID; can be customized using an external EEPROM (see Table 23)                     |

| 12                | bcdDevice          | 2               | 01, 01         | device release 1.1; silicon revision increments this value                                         |

| 14                | iManufacturer      | 1               | 00             | no manufacturer string (default)                                                                   |

|                   |                    |                 | [01]           | manufacturer string enabled (using an external EEPROM)                                             |

| 15                | iProduct           | 1               | 00             | no product string (default)                                                                        |

|                   |                    |                 | [02]           | product string enabled (using an external EEPROM)                                                  |

| 16                | iSerialNumber      | 1               | 00             | no serial number string                                                                            |

| 17                | bNumConfigurations | 1               | 01             | one configuration                                                                                  |

|                   |                    |                 |                |                                                                                                    |

Table 11: Configuration descriptor

Values in square brackets are optional.

| Offset<br>(bytes) | Field name          | Size<br>(bytes) | Value<br>(Hex) | Comments                                                                     |

|-------------------|---------------------|-----------------|----------------|------------------------------------------------------------------------------|

| 0                 | bLength             | 1               | 09             | descriptor length = 9 bytes                                                  |

| 1                 | bDescriptorType     | 1               | 02             | type = CONFIGURATION                                                         |

| 2                 | wTotalLength        | 2               | 19, 00         | total length of configuration, interface and endpoint descriptors (25 bytes) |

| 4                 | bNumInterfaces      | 1               | 01             | one interface                                                                |

| 5                 | bConfigurationValue | 1               | 01             | configuration value = 1                                                      |

| 6                 | iConfiguration      | 1               | 00             | no configuration string                                                      |

| 7                 | bmAttributes        | 1               | E0             | self-powered with remote wake-up [1]                                         |

|                   |                     |                 | A0             | bus-powered with remote wake-up [1]                                          |

| 8                 | MaxPower [2]        | 1               | 32             | 100 mA (default)                                                             |

|                   |                     |                 | [00]           | 0 mA (using an external EEPROM)                                              |

|                   |                     |                 | [FA]           | 500 mA (using an external EEPROM)                                            |

<sup>[1]</sup> Selected by input SP/BP.

Table 12: Interface descriptor

| Offset<br>(bytes) | Field name         | Size<br>(bytes) | Value<br>(Hex) | Comments                           |

|-------------------|--------------------|-----------------|----------------|------------------------------------|

| 0                 | bLength            | 1               | 09             | descriptor length = 9 bytes        |

| 1                 | bDescriptorType    | 1               | 04             | type = INTERFACE                   |

| 2                 | bInterfaceNumber   | 1               | 00             | -                                  |

| 3                 | bAlternateSetting  | 1               | 01             | no alternate setting               |

| 4                 | bNumEndpoints      | 1               | 01             | status change (interrupt) endpoint |

| 5                 | bInterfaceClass    | 1               | 09             | HUB_CLASSCODE                      |

| 6                 | bInterfaceSubClass | 1               | 00             | -                                  |

| 7                 | bInterfaceProtocol | 1               | 00             | no class-specific protocol         |

| 8                 | bInterface         | 1               | 00             | no interface string                |

Table 13: Endpoint descriptor

|                   | <u> </u>         |                 |                |                             |

|-------------------|------------------|-----------------|----------------|-----------------------------|

| Offset<br>(bytes) | Field name       | Size<br>(bytes) | Value<br>(Hex) | Comments                    |

| 0                 | bLength          | 1               | 07             | descriptor length = 7 bytes |

| 1                 | bDescriptorType  | 1               | 05             | type = ENDPOINT             |

| 2                 | bEndpointAddress | 1               | 81             | endpoint 1, direction: IN   |

| 3                 | bmAttributes     | 1               | 03             | interrupt endpoint          |

| 4                 | wMaxPacketSize   | 2               | 01, 00         | packet size = 1 byte        |

| 6                 | bInterval        | 1               | FF             | polling interval (255 ms)   |

<sup>[2]</sup> Value in units of 2 mA.

Table 14: Hub descriptor

Values in square brackets are optional.

| Offset<br>(bytes) | Field name            | Size<br>(bytes) | Value<br>(Hex)                                                          | Comments                                                                               |

|-------------------|-----------------------|-----------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 0                 | bDescLength           | 1               | 09                                                                      | descriptor length = 9 bytes                                                            |

| 1                 | bDescriptorType       | 1               | 29                                                                      | type = HUB                                                                             |

| 2                 | bNbrPorts             | 1               | 05 to 02                                                                | number of enabled downstream ports; selectable by DP/DM strapping                      |

| 3                 | 3 wHubCharacteristics | 2               | 09, 00                                                                  | individual power switching [1], overcurrent protection active (modes 0, 1, 3, 4, 5, 7) |

|                   |                       |                 | 11, 00                                                                  | individual power switching [1], no overcurrent protection (modes 2, 6) [2]             |

| 5                 | bPwrOn2PwrGood [3]    | 1               | 32                                                                      | 100 ms (default; modes 0, 1, 2, 4, 5, 6)                                               |

|                   |                       |                 | 00                                                                      | 0 ms (default; modes 3, 7)                                                             |

|                   | [FA]                  | [FA]            | 500 ms (using an external EEPROM; modes 0, 1, 2, 4, 5, 6); see Table 23 |                                                                                        |

| 6                 | bHubContrCurrent      | 1               | 64                                                                      | maximum hub controller current (100 mA)                                                |

| 7                 | DeviceRemovable       | 1               | 00                                                                      | all devices removable                                                                  |

| 8                 | PortPwrCtrlMask       | 1               | FF                                                                      | must be all ones for compatibility with USB Specification Rev. 1.0                     |

<sup>[1]</sup> ISP1122A always reports power management status on an individual basis, even for ganged/global modes. This is compliant with USB Specification Rev. 1.1.

#### Table 15: String descriptors

String descriptors are optional and therefore disabled by default; they can be enabled through an external EEPROM.

| Offset (bytes) | Field name                                 | Size<br>(bytes) | Value<br>(Hex)    | Comments                     |  |  |

|----------------|--------------------------------------------|-----------------|-------------------|------------------------------|--|--|

| String d       | escriptor (0): language                    | ID string       |                   |                              |  |  |

| 0              | bLength                                    | 1               | 04                | descriptor length = 4 bytes  |  |  |

| 1              | bDescriptorType                            | 1               | 03                | type = STRING                |  |  |

| 2              | bString                                    | 2               | 09, 04            | LANGID code zero             |  |  |

| String d       | String descriptor (1): manufacturer string |                 |                   |                              |  |  |

| 0              | bLength                                    | 1               | 2E                | descriptor length = 46 bytes |  |  |

| 1              | bDescriptorType                            | 1               | 03                | type = STRING                |  |  |

| 2              | bString                                    | 44              | UC[1]             | "Philips Semiconductors"     |  |  |

| String d       | escriptor (2): product s                   | string          |                   |                              |  |  |

| 0              | bLength                                    | 1               | 10                | descriptor length = 16 bytes |  |  |

| 1              | bDescriptorType                            | 1               | 03                | type = STRING                |  |  |

| 2              | bString                                    | 14              | UC <sup>[1]</sup> | "ISP1122"                    |  |  |

<sup>[1]</sup> Unicode encoded string.

<sup>[2]</sup> Condition with no overcurrent detection is reported to the host.

<sup>[3]</sup> Value in units of 2 ms.

### 9.4 Hub responses

This section describes the hub responses to requests from the USB host.

#### 9.4.1 Get device status

The hub returns 2 bytes, see Table 16.

Table 16: Get device status response

| Bit #   | Function       | Value | Description            |

|---------|----------------|-------|------------------------|

| 0       | self-powered   | 0     | bus-powered            |

|         |                | 1     | self-powered           |

| 1       | remote wake-up | 0     | no remote wake-up      |

|         |                | 1     | remote wake-up enabled |

| 2 to 15 | reserved       | 0     | -                      |

### 9.4.2 Get configuration

The hub returns 1 byte, see Table 17.

Table 17: Get configuration response

| Bit#   | Function            | Value | Description           |

|--------|---------------------|-------|-----------------------|

| 0      | configuration value | 0     | device not configured |

|        |                     | 1     | device configured     |

| 1 to 7 | reserved            | 0     | -                     |

#### 9.4.3 Get interface status

The hub returns 2 bytes, see Table 18.

Table 18: Get interface status response

| Bit#    | Function | Value | Description |

|---------|----------|-------|-------------|

| 0 to 15 | reserved | 0     | -           |

### 9.4.4 Get hub status

The hub returns 4 bytes, see Table 19.

Table 19: Get hub status response

| Bit #    | Function                     | Value | Description                        |

|----------|------------------------------|-------|------------------------------------|

| 0        | 0 local power source         |       | local power supply good            |

|          |                              |       | local power supply lost            |

| 1        | overcurrent indicator        | 0     | no overcurrent condition           |

|          |                              | 1     | hub overcurrent condition detected |

| 2 to 15  | reserved                     | 0     | -                                  |

| 16       | local power status change    | 0     | no change in local power status    |

|          |                              | 1     | local power status changed         |

| 17       | overcurrent indicator change | 0     | no change in overcurrent condition |

|          |                              | 1     | overcurrent condition changed      |

| 18 to 31 | reserved                     | 0     | -                                  |

# 9.4.5 Get port status

The hub returns 4 bytes. The first 2 bytes contain the port status bits (wPortStatus, see Table 20). The last 2 bytes hold the port status change bits (wPortChange, see Table 21).

Table 20: Get port status response (wPortStatus)

| Bit#     | Function                  | Value | Description                    |

|----------|---------------------------|-------|--------------------------------|

| 0        | current connect status    | 0     | no device present              |

|          |                           | 1     | device present on this port    |

| 1        | port enabled/disabled     | 0     | port disabled                  |

|          |                           | 1     | port enabled                   |

| 2        | suspend                   | 0     | port not suspended             |

|          |                           | 1     | port suspended                 |

| 3        | overcurrent indicator     | 0     | no overcurrent condition       |

|          |                           | 1     | overcurrent condition detected |

| 4        | reset                     | 0     | reset not asserted             |

|          |                           | 1     | reset asserted                 |

| 5 to 7   | reserved                  | 0     | -                              |

| 8        | port power                | 0     | port powered off               |

|          |                           | 1     | port power on                  |

| 9        | low-speed device attached | 0     | full-speed device attached     |

|          |                           | 1     | low-speed device attached      |

| 10 to 15 | reserved                  | 0     | -                              |

|          |                           |       |                                |

Table 21: Get port status response (wPortChange)

| Bit #   | Function                     | Value | Description                         |

|---------|------------------------------|-------|-------------------------------------|

| 0       | 0 connect status change      |       | no change in current connect status |

|         |                              | 1     | current connect status changed      |

| 1       | port enabled/disabled        |       | no port error                       |

|         | change                       | 1     | port disabled by a port error       |

| 2       | suspend change               |       | no change in suspend status         |

|         |                              | 1     | resume complete                     |

| 3       | overcurrent indicator change | 0     | no change in overcurrent status     |

|         |                              | 1     | overcurrent indicator changed       |

| 4       | reset change                 | 0     | no change in reset status           |

|         |                              | 1     | reset complete                      |

| 5 to 15 | reserved                     | 0     | -                                   |

#### 9.4.6 Get configuration descriptor

The hub returns 25 bytes containing the configuration descriptor (9 bytes, see Table 11), the interface descriptor (9 bytes, see Table 12) and the endpoint descriptor (7 bytes, see Table 13).

#### 9.4.7 Get device descriptor

The hub returns 18 bytes containing the device descriptor, see Table 10.

#### 9.4.8 Get hub descriptor

The hub returns 9 bytes containing the hub descriptor, see Table 14.

#### 9.4.9 Get string descriptor (0)

The hub returns 4 bytes containing the language ID, see Table 15.

# 9.4.10 Get string descriptor (1)

The hub returns 46 bytes containing the manufacturer name, see Table 15.

### 9.4.11 Get string descriptor (2)

The hub returns 16 bytes containing the product name, see Table 15.

# 10. I<sup>2</sup>C-bus interface

A simple I<sup>2</sup>C-bus interface is provided in the ISP1122A to read customized vendor ID, product ID and some other configuration bits from an external EEPROM. The interface supports single master operation at a nominal bus speed of 93.75 kHz.

The I<sup>2</sup>C-bus interface is intended for bidirectional communication between ICs via two serial bus wires, SDA (data) and SCL (clock). Both lines are driven by open-drain circuits and must be connected to the positive supply voltage via pull-up resistors.

#### 10.1 Protocol

The I<sup>2</sup>C-bus protocol defines the following conditions:

- Bus free: both SDA and SCL are HIGH

- START: a HIGH-to-LOW transition on SDA, while SCL is HIGH

- STOP: a LOW-to-HIGH transition on SDA, while SCL is HIGH

- Data valid: after a START condition, data on SDA are stable during the HIGH period of SCL; data on SDA may only change while SCL is LOW.

Each device on the I<sup>2</sup>C-bus has a unique slave address, which the master uses to select a device for access.

The master starts a data transfer using a START condition and ends it by generating a STOP condition. Transfers can only be initiated when the bus is free. The receiver must acknowledge each byte by means of a LOW level on SDA during the ninth clock pulse on SCL.

For detailed information please consult *The I<sup>2</sup>C-bus and how to use it.*, order number 9398 393 40011.

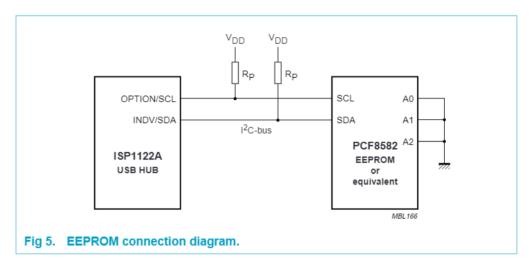

#### 10.2 Hardware connections

Via the I<sup>2</sup>C-bus interface the ISP1122A can be connected to an external EEPROM (PCF8582 or equivalent). The hardware connections are shown in Figure 5.

The SCL and SDA pins are multiplexed with pins OPTION and INDV respectively.

The slave address which ISP1122A uses to access the EEPROM is 1010000B. Page mode addressing is not supported, so pins A0, A1 and A2 of the EEPROM must be connected to GND (logic 0).

#### 10.3 Data transfer

When the ISP1122A is reset, the  $I^2C$ -bus interface tries to read 6 bytes of configuration data from an external EEPROM. If no response is detected, the levels on inputs SDA and SCL are interpreted as INDV and OPTION to select the operating mode (see Table 4).

The data in the EEPROM memory are organized as shown in Table 22.

Table 22: EEPROM organization

| Address<br>(Hex) | Default value (Hex) | Contents                                  |

|------------------|---------------------|-------------------------------------------|

| 00               | CC                  | idVendor <sup>[1]</sup> (lower byte)      |

| 01               | 04                  | idVendor <sup>[1]</sup> (upper byte)      |

| 02               | 22                  | idProduct <sup>[2]</sup> (lower byte)     |

| 03               | 11                  | idProduct <sup>[2]</sup> (upper byte)     |

| 04               | -                   | configuration bits C7 to C0; see Table 23 |

| 05               | AA                  | signature                                 |

<sup>[1]</sup> Vendor ID code in the Device descriptor, see Table 10.

<sup>[2]</sup> Product ID code in the Device descriptor, see Table 10.

**Table 23: Configuration bits**

| to logic 0                  |

|-----------------------------|

| to logic 0                  |

| to logic 0                  |

|                             |

| 32H)                        |

| FAH)                        |

|                             |

| ings:<br>P1122A")           |

| tection<br>ns OCn<br>level) |

| tection                     |

|                             |

|                             |

|                             |

|                             |

- [1] Default value at reset if no external EEPROM is present.

- [2] Modifies the Hub Descriptor field 'bPwrOn2PwrGood', see Table 14.

- [3] Modifies the Hub Descriptor field 'MaxPower', see Table 14.

# 11. Hub power modes

USB hubs can either be self-powered or bus-powered.

**Self-powered** — Self-powered hubs have a 5 V local power supply on board which provide power to the hub and the downstream ports. The *USB Specification Rev. 1.1* requires that these hubs limit the current to 500 mA per downstream port and report overcurrent conditions to the host. The hub may optionally draw 100 mA from the USB supply (V<sub>BUS</sub>) to power the interface functions (**hybrid-powered**).

**Bus-powered** — Bus-powered hubs obtain all power from the host or an upstream self-powered hub. The maximum current is 100 mA per downstream port. Current limiting and reporting of overcurrent conditions are both optional.

Power switching of downstream ports can be done **individually** or **ganged**, where all ports are switched simultaneously with one power switch. The ISP1122A supports both modes, which can be selected using input INDV (see Table 4).

# 11.1 Voltage drop requirements

#### 11.1.1 Self-powered hubs

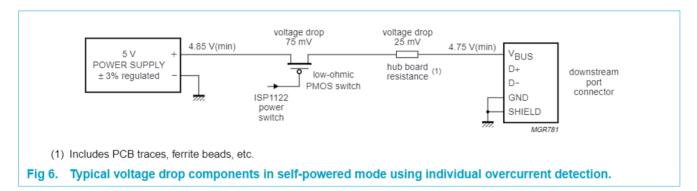

Self-powered hubs are required to provide a minimum of 4.75 V to its output port connectors at all legal load conditions. To comply with Underwriters Laboratory Inc. (UL) safety requirements, the power from any port must be limited to 25 W (5 A at 5 V). Overcurrent protection may be implemented on a global or individual basis.

Assuming a 5 V  $\pm$  3% power supply the worst case supply voltage is 4.85 V. This only allows a voltage drop of 100 mV across the hub printed-circuit board (PCB) to each downstream connector. This includes a voltage drop across:

- Power supply connector

- Hub PCB (power and ground traces, ferrite beads)

- Power switch (FET on-resistance)

- Overcurrent sense device.

PCB resistance and power supply connector resistance may cause a drop of 25 mV, leaving only 75 mV as the voltage drop allowed across the power switch and overcurrent sense device. The individual voltage drop components are shown in Figure 6.

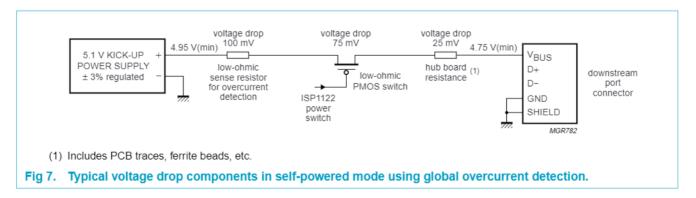

In case of global overcurrent detection an increased voltage drop is needed for the overcurrent sense device (in this case a low-ohmic resistor). This can be realized by using a special power supply of 5.1 V  $\pm$  3%, as shown in Figure 7.

#### 11.1.2 Bus-powered hubs

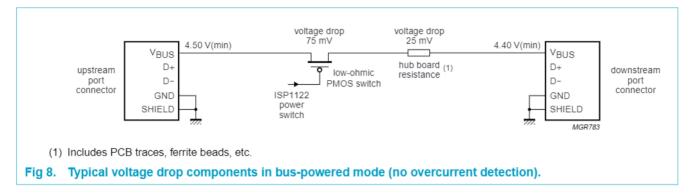

Bus-powered hubs are guaranteed to receive a supply voltage of 4.5 V at the upstream port connector and must provide a minimum of 4.4 V to the downstream port connectors. The voltage drop of 100 mV across bus-powered hubs includes:

- Hub PCB (power and ground traces, ferrite beads)

- Power switch (FET on-resistance)

- Overcurrent sense device.

The PCB resistance may cause a drop of 25 mV, which leaves 75 mV for the power switch and overcurrent sense device. The voltage drop components are shown in Figure 8.

For bus-powered hubs overcurrent protection is optional. It may be implemented for all downstream ports on a global or individual basis.

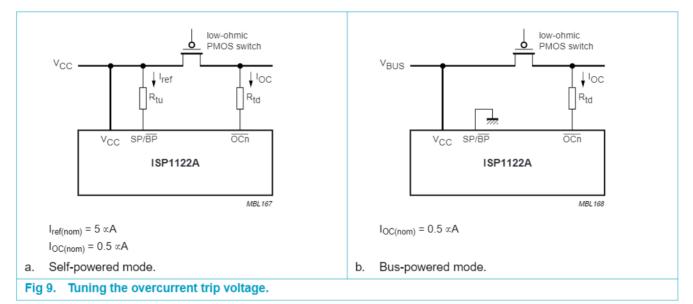

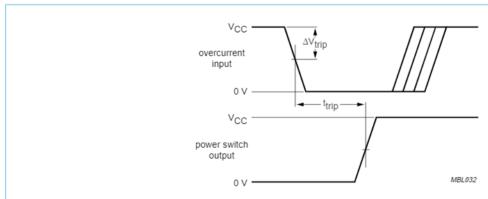

### 12. Overcurrent detection

The ISP1122A has an analog overcurrent detection circuit for monitoring downstream port lines. This circuit automatically reports an overcurrent condition to the host and turns off the power to the faulty port. The host must reset the condition flag.